SPS CPU-Design, Architektur und Emulation?

Ich beschäftige mich schon etwas länger mit SPS, jedoch nur in der Theorie.

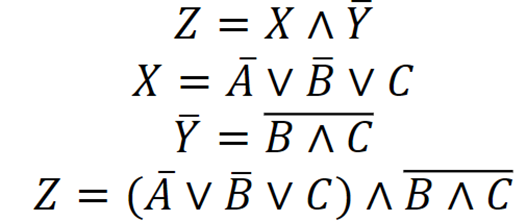

Eine SPS arbeitet ja zyklisch. Also es werden seriell (?) alle 1-Bit Eingänge abgefragt (mit Eingabeverzögerung), dann Merker und Co gelesen und erst dann verarbeitet. Ist das nicht furchtbar langsam?

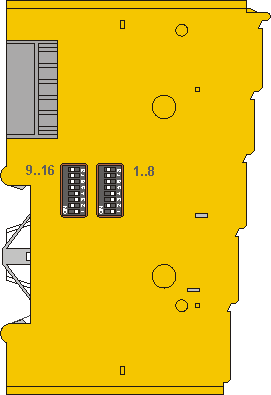

Über die CPU findet man kaum bzw andere Angaben. Nach Recherchen hatten (zumindest) ältere SPS herkömmliche CPUs, wie 8051. Oder waren die für andere Zwecke als für den normalem Ablauf ?

Eine normale CPU könnte doch parallel einlesen, bzw arbeiten. Bei Mehrkern sowieso. Wie ist denn das Design und Architektur der CPU? Von Neumann? Und wie der genaue Ablauf?

Vermutlich gibt es erst einen Speichertest, dann eine Initialisierung, Modi-Abfrage (Programmierung), Tasten-Abfragen usw. Und dann die Abfrage der Eingänge. Die Verarbeitung wird je nach Hersteller stark variieren.

Wie würde eine Emulation ablaufen und macht die überhaupt Sinn? Neben der SPS müsste man ja die angeschlossenen Geräte emulieren und zudem noch das Programmiergerät. Gibt es da Beispiele? Oder nur Simulationen?