Wie funktioniert das NICHT-Gatter mit FETs?

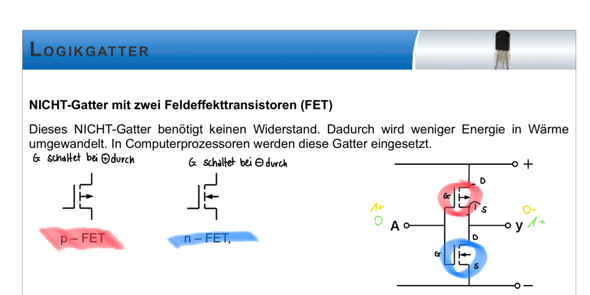

Wir haben seit letzer Zeit mit dem FETs gearbeitet und ich konnte das Thema noch nicht so richtig verstehen. Nun haben wir auch noch NICHT-Gatter hinzugefügt und ich habe seitdem keinen Plan mehr. Zum einem verstehe ich nicht wie ein NICHT-Gatter bei solchen Schaltungen funktionieren soll und zum anderen weiß ich auch nicht wie es mit dem Potenzial funktioniert, also wieso sie mal positiv oder negativ sein können (hier im Bild als 0 und 1 dargestellt). Auch versteh ich nicht was durchschalten bedeutet und wieso bestimmte Ladungen erzeugen, dass Gate durchschaltet. Ich entschuldige mich, dass ich keine konkreteren Fragen stellen kann, aber ich versteh zur Zeit nur sehr wenig über die Themen.

2 Antworten

Zur Frage warum eine Ladung den Fet durchschaltet verweise ich auf den Wikipedia Artikel zur Funktionsweise von FETs.

Die Schaltung funktioniert im wesentlichen genau so in Transistorlogik mit Totem Pole Ausgang.

Bei High am Eingang sperrt der ober P Fet und der unter N Fet leitet damit ist der Ausgang Low. Bei Low am Eingang ists anders rum.

Der P Fet verhält sich dabei ähnlich einem PNP Transistor der N Fet ähnlich einem NPN Transistor.

Durchschalten bedeutet dass die Drain Source Strecke niederohmig wird.

Wenn A - der Eingang + hat, sperrt der n-FET und

der p-FET öffnet.

Das bedeutet H am Eingang, auch H am Ausgang

Ein L am Eingang sperrt p-FET und öffnet n-FET

das Bedeutet L am Eingang gleich L am Ausgang. Da fehlt die Invertierung.

Wir haben im Unterricht noch nie die Begriffe High und Low benutzt, was bedeuten sie?