Sequentielle Logik mit Zeiverlaufsidagramm?

Hallo

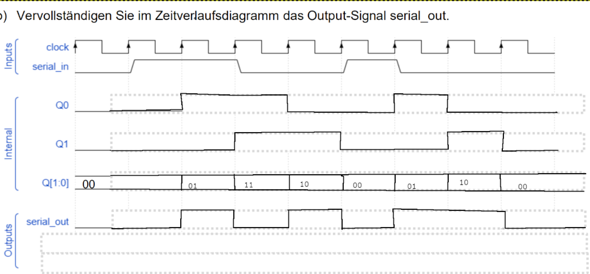

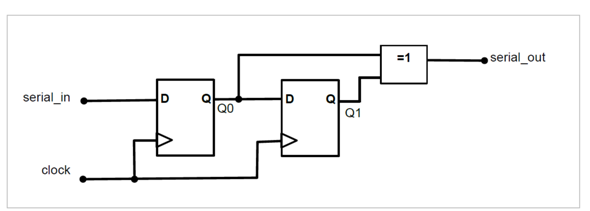

Ich habe folgendes Zeiverlaufsidagramm:

Fragen:

Bei c weiss ich nicht was der Zusammenhang ist und bei d hätte ich gesagt, dass jedes signal_in zuerst bis zum signal_out vollständig übertragen werden muss und erst dann, dass nächste Signal verarbeitet werden kann, d.h. serial_in -> Q0 -> Q1 -> serial_out

Plan:

2 Antworten

Was meinst du mit

Bei c weiss ich nicht was der Zusammenhang ist

Ich kenne Teil a) und b) nicht, aber hast du mal eine Wahrheitstabelle aufgestellt?

Und dann die Aufforderung aus c)

"Beobachten sie Zusammenhang zwischen serial_in und serial_out" durchgeführt.

Was ist der Zusammenhang an einem Getränkeautomat?

Du schmeißt Geld rein und ein Getränk kommt heraus.... ;)

Zunächst aber mal. Die Grafik ist korrekt.

@Destranix: =1 ist EXOR und keine Verundung, daher passt es auch.

Wenn wir Serial_In und Serial_Out in Bezug zueinander setzen, dann sehen wir das wir ein Taktgesteuerten positiv und negative Flankendetektor haben.

Das Dateineingangssignal wird also so lange verzögert, bis es synchron zum Takt liegt. Wie das funktioniert sieht man ja ganz gut am Bild: Bis zur nächsten aktiven Taktflanke wird der aktuelle Zustand gehalten (verzögert)

zu d):

Da wir also durch den Takt eine Art Vorgabe erhalten, liegt hier auch der große "Vorteil" der typisch für so eine Schaltung ist:

Vorgänge unterschiedlicher Bauteile mit unterschiedlicher Reaktionszeit(Verzögerung) werden hier miteinander zum Takt synchronisiert.

Ich würd esagen das zeigt an, wenn das Serial_in den selben Zustand hat wie im letztem Clock-Cycle.

Serial_out hast du dabei wohl falsch berechnet, für die letzten Takte, wo das 01 une 10 ist, sollte da 0 rauskommen, da du ja verundest.

Zudem bin ich mir nicht sicher, ob du nicht schon jeweils einen Takt früher den Wert im Register setzen solltest, das hängt aber davon ab, wann genau das Register dne Wert übernimmt (ob bei steigender oder fallender Flanke).

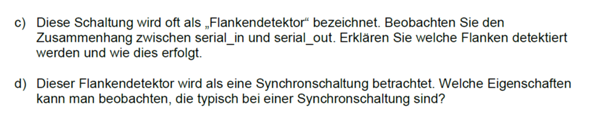

Zu c):

Die Flanke wird detektiert, indem der aktuelle Eingabewert mit dem des vorherigem Clock-Cycles verglichen wird.

Detektiert werden sowohl steigende als auch fallende Flanken.

Zu d):

Da bin ich mir nicht sicher, was gefragt ist. Ich würde sagen, wesentlich ist, dass die register gleichzeitig/synchron schalten und auch immer nur einmal.