Wie erweitere ich einen Eintaktprozessor richtig?

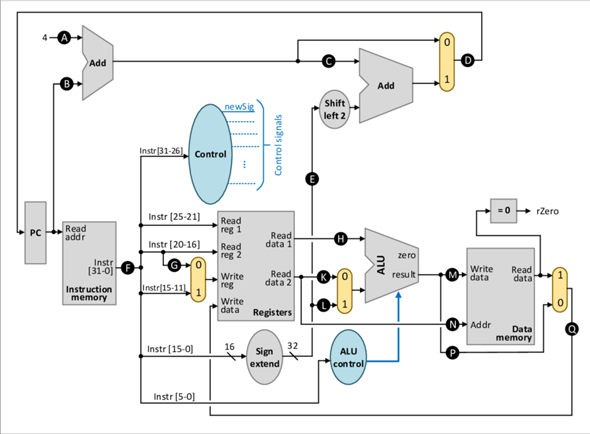

Gehen wir davon aus, dass wir einen Eintaktprozessor haben. Nun soll der Eintaktprozessor so erweitert werden, dass er nach der Erweiterung auch einen neuen bestimmten Befehl ebenfalls ausführen kann. Dafür muss ich verstehen, wie all diese Komponenten zusammenhängen, um genau zu wissen, wo ich meinen neuen "Baustein" für den neuen Befehl hinzufügen kann.

Zum Beispiel kann dieser Eintaktprozessor die "add"-Operation ausführen, da er über Register-Dateien, einen Addierer, eine ALU, einen Multiplexer usw. verfügt. Da der Datenpfad für die "add"-Operation, die Operanden von den Registern zum Addierer leitet, das Ergebnis durch die ALU berechnet, und schließlich das Ergebnis in das Zielregister zurückführt...

Nun habe ich eine Beispiel-Aufgabe mit einer Lösung, bin mir aber unsicher, wie man zu dieser Lösung gelangt. Könnte mir jemand das erklären?

In dieser Aufgabe sollen Sie den dargestellten MIPS-Eintaktprozessor erweitern, sodass der neue Befehl Read Word Until Zero (rwuz) unterstützt wird. Der abgebildete Prozessor unterscheidet sich leicht von dem Ihnen bekannten Eintaktprozessor.

rwuz unterscheidet sich von anderen MIPS-Befehlen dadurch, dass er von dem Prozessor automatisch mehrfach ausgeführt werden soll, solange das gelesene Datenwort nicht null war.

rwuz soll ein Befehl im I-Format sein.

Für rwuz soll der Opcode 0x11 verwendet werden.

Der Direktoperand (immediate) soll zu dem rs-Register hinzuaddiert werden. Das Ergebnis dieser Operation soll im rt-Register gespeichert werden.

Das rt-Register soll gleichzeitig als Adresse für einen Lesezugriff auf den Datenspeicher verwendet werden.

Solange der gelesene Wert aus dem Speicher nicht null ist, soll der selbe rwuz-Befehl im nächsten Taktzyklus erneut ausgeführt werden (PC bleibt gleich). Falls der gelesene Datenwert null ist, soll die nächste Instruktion ausgeführt werden (PC um 4 erhöhen).

Das aus dem Speicher gelesene Datenwort soll nicht in einem Register abgelegt werden.

Tipp: Das Signal rZero zeigt an, ob das aus dem Speicher gelesene Datenwort null ist

Selbst wenn niemand in der Lage ist, mir dies genau zu erklären, kann mir jemand Quellen, Videos oder Bücher empfehlen, damit ich ein besseres Verständnis dafür entwickeln kann?

2 Antworten

Folgende Überlegung:

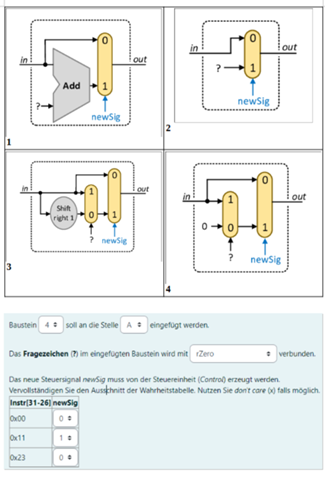

Die Spezifikation des neuen Befehls sagt, daß der PC über mehrere Takte konstant (0) bleiben muß und wenn eine 0 gelesen wird, um 4 erhöht wird. D.h. Du brauchst anstatt der fixen 4 an Stelle A etwas, das entweder die 4 oder eine 0 liefert, also einen MUX, der von dem entsprechenden Steuersignal angesteuert wird.....

Bzw. solltest Du merken:

Ich habe je nach Situation eine 4 oder eine 0, die auf den PC addiert wird, eine 4 für Alle ISNs außer der neuen, wenn die neue ISN ausgeführt wird je nach Situation 0 oder 4 in Abhängigkeit eines (weiteren) Steuersignals.

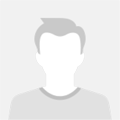

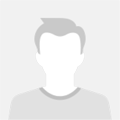

Also wirst Du einen MUX für die beiden Fälle der neuen ISN benötigen, der in Abhängigkeit des erreichens der 0 eine 4 ausgibt und mit einem weiteren MUX, der zwischen dieser ISN und allen ANDEREN (fixe 4) umschaltet.

Insofern kommen nur noch 3+4 in Frage, wobei nicht zu sehen ist, welche Aufgabe der Shifter hat (Wenn überhaupt könnte man mit diesen nach Bedarf eien 4 zu ner 0 shiften anstatt zu muxen - wäre aber auch ein wenig drüber).

----------

Unbesehens der konkreten Aufgabe (ist ja nicht Deine erste Frage), kannst Du mal nach Vorlesungsskripten zum Thema schauen (einen Link hast Du schon). Ferner würde ich mir mal anschauen, wie eine FSMD (Finite State Machine with Datapath) so aussieht. Diese ist quasi um die freie Programmierbarkeit beraubt, sodaß man sich erstmal besser die grundlegende Funktionsweise von Datenpfaden und deren Ansteuerung anschauen kann.

Der endliche Automat kodiert das feste Programm.

Für diese Anforderung benötigen wir also auf jeden Fall mindestens einen MUX, der überprüft, ob die Adresse im Datenspeicher gleich 0 oder 1 ist. Basierend auf dem Text wissen wir, dass dieses Signal "rZero" genannt wird.

Ich würde einem MUX nicht die Fähigkeit des "Prüfens" zusprechen wollen. die Prüfung auf 0 macht ja 'irgendwas anderes' und der MUX erhält entsprechend dann den Stimulus (Steuersignal) rZero basierend auf der eigentlichen Prüfung.

rZero steuert also den MUX, der daraufhin einen Eingang für den gewünschten Festwert wählt.

Direkt drauf ist nochmal eine ähnliche Formulierung, da solltest Du auch nochmal ran.

Randnotiz: Ich würde also Plural MUXes schreiben, das lässt sich sonst so schlecht sprechen ;-).

Denn wir wissen, dass der PC vom Addierer erhöht wird,

vielleicht besser 'von diesem Addierer', sonst kommt man vielleicht auf die Idee es könnte der allgemeine Addierer in der ALU sein.

Vielen Dank für die Hilfe! Es war wirklich sehr hilfreich. Ich werde dir den Stern geben, sobald die 24 Stunden vorbei sind.

Die Frage sprengt das was ich in Textform bereit bin zu schreiben

Ohne Erklärungen: Der Befehl an der Adresse die im program counter steht wird geladen, der opcode (Teil des Befehls) wird dekodiert und löst das zugehörige Steuer Signal new signal aus (Daher new signal nur für den entsprechenden opcode 1). Das aktiviert einen Multiplexer der dafür sorgt, dass nicht mehr wie sonst grundsätzlich in jedem Takt 4 auf den program counter addiert wird, sondern nurnoch wenn der gelesene Wert nicht 0 ist (das ist das Signal das bei ? anliegt rZero)

Ich mag die Vorlesung nicht, aber sie deckt vermutlich alles ab (außer die zugrunde liegenden Logikgatter und Volladdierer und Zähler etc.): https://youtube.com/playlist?list=PLfk0Dfh13pBMh-5TcPtx-3bXAwnDnKTME&si=_rkVkEvGSSGR-8mL

Geht vermutlich zu sehr in die Tiefe, einiges kannst du sicherlich skippen

Hallo, vielen Dank für die Antwort. Ich habe noch einmal versucht, es selbst in Worte zu fassen und wollte fragen, ob es vielleicht möglich wäre, kurz darüber zu schauen, ob die Erklärung damit richtig ist oder ob ich immer noch etwas missverstanden habe.:

"Anhand der Spezifikationen können wir mehrere Aspekte für die Erweiterung "rwuz" herauslesen.

Zunächst soll das Immediate zum "rs"-Register addiert und dann im "rt"-Register gespeichert werden. Dies entspricht dem bereits vorhandenen "addi"-Befehl (addi rt, rs, immediate) in unserem Eintaktprozessor, bei dem die ALU die Addition durchführt. Daher ist keine Änderung erforderlich.

Allerdings soll das "rt"-Register auch als Adresse für einen Lesezugriff auf den Datenspeicher dienen. Und solange der gelesene Speicherwert nicht null ist, soll "rwuz" erneut ausgeführt werden. Für diese Anforderung benötigen wir also auf jeden Fall mindestens einen MUX, der überprüft, ob die Adresse im Datenspeicher gleich 0 oder 1 ist. Basierend auf dem Text wissen wir, dass dieses Signal "rZero" genannt wird.

Wir wissen auch, dass wir mindestens einen weiteren MUX benötigen, der überprüft, ob unsere neue Anweisung ("rwuz") überhaupt erneut ausgeführt werden soll oder nicht. Denn falls ja, soll der PC gleich bleiben und falls nein, soll der PC sich um 4 erhöhen.

Also wissen wir nun, dass wie zwei MUXs benötigen. Abbildung 3 und 4 haben 2 MUXs, wobei jedoch kein Shifter wie von Abbildung 3 nötig ist, somit ist die klare Wahl Abbildung 4.

Als nächstes stellt sich die Frage, wo wir diesen Baustein einsetzen sollen. Gemäß der Anforderung: "Falls der gelesene Datenwert null ist, soll die nächste Instruktion ausgeführt werden (PC um 4 erhöhen)" sollte es in "A" eingesetzt werden. Denn wir wissen, dass der PC vom Addierer erhöht wird, und dass diese immer +4 Byte rechnet (da jeder Befehl normalerweiße 4 Byte groß ist). Und da der Output von unseren beiden MUXs entscheidet, ob es erhöht werden soll oder nicht, setzten wir es vor den Addierer.

Abschließend wird gefragt, welche Anweisungen bei "newsig" auf 1, 0 oder "don't care" gesetzt werden müssen. Wie oben erwähnt wurde, hat "newsig" den Opcode 0x11. Daher setzen wir diesen auf 1 und alles andere auf 0."