Hazards in einer Schaltung finden?

Hallo,

ich soll in einer Schaltung Hazards finden. Die Lösung zu der Aufgabe habe ich bereits, aber ich hoffe mir kann jemand erklären wieso genau das die Lösung ist

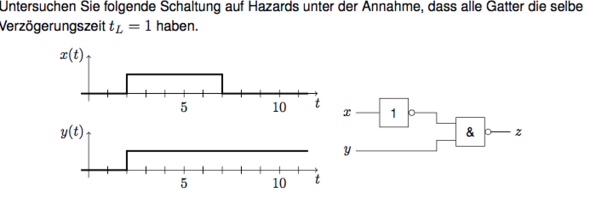

Aufgabe:

4 Antworten

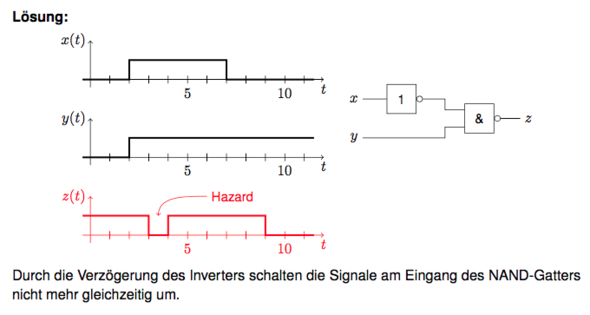

*hust hust* Die Lösung steht darunter! :

Zitat: Durch die Verzögerung des Inverters schalten die Signale am Eingang des NAND-Gatters nicht mehr gleichzeitig.

Ich versuche das nochmal näher zu erläutern:

Gatter in der Theorie schalten einfach durch ohne Zeitverzögerung. Sowas gibts aber in der Praxis nicht. Normale TTL-Schaltgatter (VCC=5V; suche mal nach den 7400. das ist ein NAND und irgendwie so der bekannteste ^^) haben eine Schaltzeit von 10ns. Schottky-TTLs sind etwas schneller und schalten um die 3ns.

Aber ist egal. Wichtig ist, dass all diese eine Schaltzeit haben.

So und jetzt kommt das wichtige:

deine theoretische Funktion lautet z= ! ( !x * y )

für den gezeigten Zustand x=1 und y=1 ist z=1, denn

not(not(true) and true) = not(false and true) = not(false) = true

Jetzt kommt aber der Haken, der halt in der Praxis da ist: Die Zeitverzögerung des Inverters!

Werden x und y gleichzeitig auf 1 geschalten (Zum Zeitpunkt t=2 im BSP), dann liegt am y-Eingang des NAND-Gatters eine 1 an, jedoch am x-Eingang des NAND-Gatters liegt noch die invertierte 0 (also 1) an, weil das Signal noch nicht durch den Inverter verarbeitet wurde.

Es liegt am NAND also eine 1(x) und 1(y) an. Und :

not( 1 * 1) = 0 (=false)

Erst nachdem der Inverter fertig invertiert hat, kommt am NAND-Gatter das eigentlich gewollte Signal an.

Und daher entsteht nach der Schaltung auch kurz so eine Flanke. Diese nennt man Hazards. Kann man aber zum Beispiel durch Redundantglieder beheben.

Ich hoffe du verstehst das jetzt.

Zeichne dir das Zeitdiagramm für die Eingänge des NAND-Gatters.

Wenn x den Zustand ändert, dauert dies einen Zyklus, bis dies beim NAND ankommt, y liegt sofort an. Deshalb liegt zum Zeitpunkt 2 am NAND eine Eingangskombination vor, die den Ausgang z abfallen lässt. Da das NAND-Gatter aber einen Zyklus braucht zum Durchschalten, entsteht der Hazard erst ab t =3.

Beim Abfallen von x hast du übrigens keinen Hazard, weil hier das Signal mit dem übereinstimmt, wie du es in einer verzögerungsfreien Schaltung hättest, "nur" eben um 2 Zyklen verzögert, da das Signal über zwei Gatter läuft.

Beim Anstieg von x erhältst du allerdings einen "Einbruch" von z, den du in einer verzögerunsfreien Schaltung gar nicht hättest.

Gibt es die Aufgabe auch auf Deutsch?

der Inverter braucht eine gewisse Zeit, damit sich an seinem Ausgang der Zustand ändert. Bis dahn ist dieser ungültig und kann u.U. ein falsches Verhalten im Gesamtkontext erzeugen.

Danke dir !!

Ja die Lösung steht da, aber jedoch konnte ich mit dieser nicht 1 prozentig etwas anfangen nur grob..